Support for new Power-Saving CPU Instructions in a future Low-Power Mobile 10mm CPU Architecture from Intel code-named "Tremont" is being added to the Linux Kernel

A series of patches sent by Intel to the kernel mailing list with code adding support for new umonitor, umwait, and tpause user wait instructions got our attention since there are no such instructions on any x86-64 CPU we've heard of. They will be available on Skyhawk Lake and Elkhart Lake CPUs based on Intel's new Tremont micro-architecture sometime next year.

Intel asset Fenghua Yu explains the advantages of the new instructions in the patch-set submitted to the Linux kernel as:

"Today, if an application needs to wait for a very short duration they have to have spinloops. Spinloops consume more power and continue to use execution resources that could hurt its thread siblings in a core with hyperthreads. New instructions umonitor, umwait and tpause allow a low power alternative waiting at the same time could improve the HT sibling perform while giving it any power headroom. These instructions can be used in both user space and kernel space."

There are details on the specific new instructions included in the patch-set:

"umonitor arms address monitoring hardware using an address. The address range is determined by using CPUID.0x5. A store to an address within the specified address range triggers the monitoring hardware to wake up the processor waiting in umwait.

umwait instructs the processor to enter an implementation-dependent optimized state while monitoring a range of addresses. The optimized state may be either a light-weight power/performance optimized state (C0.1 state) or an improved power/performance optimized state (C0.2 state).

tpause instructs the processor to enter an implementation-dependent optimized state C0.1 or C0.2 state and wake up when time-stamp counter reaches specified timeout."

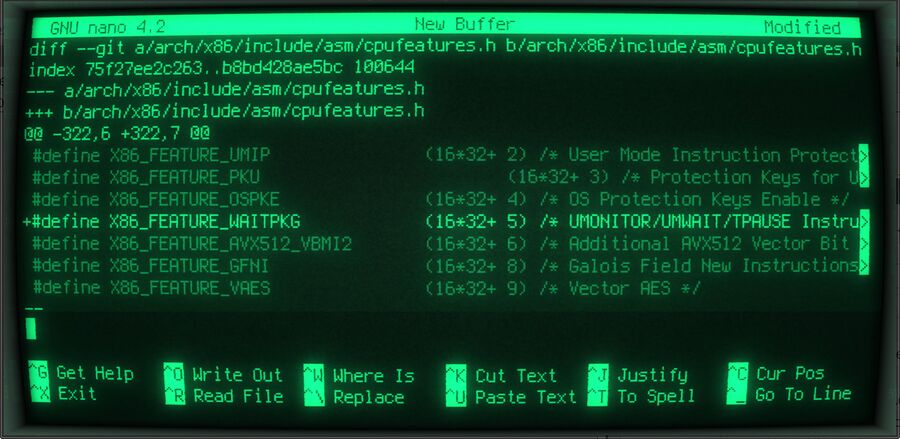

Availability of the instructions will by the kernel be indicated as X86_FEATURE_WAITPKG. A separate patch-set by Intel asset Tao Xu adds KVM supports for the new instructions.

A Intel document titled Intel® Architecture Instruction Set Extensions and Future Features Programming Reference which was, according to it's meta-data, created May 20th 2019 using Acrobat Distiller 19.0 on Windows lists the instructions "User wait: TPAUSE, UMONITOR, UMWAIT" as becoming available "TBD Future, Tremont".

So what's a "Tremont"? Wikichip lists it as "Intel's successor to Goldmont Plus, a 14 nm or 10 nm microarchitecture for ultra-low power devices and microservers". The specific chips using this new architecture are code-named "Skyhawk Lake" and "Elkhart Lake".

Skyhawk Lake CPUs will target embedded devices, tablets and low-cost notebooks while Elkhart Lake targets ultra-low power servers. These are devices where more power-efficient wait instructions can make a real difference.

Leaked Intel road-maps have indicated that these chips will be available second half of 2020. That may not be entirely accurate given that Intel's adding Linux Kernel support now. It will probably make it into Linux 5.3. That makes it more likely that these new lower-power 10nm chips will be in products on store shelves late this year or early 2020.

The full patch-set for adding the general kernel can be read at https://lkml.org/lkml/2019/6/19/972 and the patch adding KVM support can be seen at https://lkml.org/lkml/2019/6/19/84

published 2019-06-20 - last edited 2019-06-20

Enable comment auto-refresher